文章编号：1005-8451（2013）05-0008-04

# 基于FPGA的高速存储器接口应用开发

周晓波，李瑞菁，赵强

(北京交通大学 电子信息工程学院，北京 100044)

**摘要：**为了便捷对复杂时序接口的高速大容量存储介质的应用，本论文提出了一种基于DDRII SDRAM的FIFO特性存储介质接口装置的设计方案。介绍了DDRII SDRAM控制器的原理及实现方法，并基于DDRII SDRAM分时复用技术对存储器接口模块进行了设计，深入分析了接口控制模块各部分的工作原理并对其进行了功能仿真和FPGA的硬件验证。经过测试，高速存储器接口控制模块实现了DDRII内存与FPGA之间的双向数据传输与交互，具有一定的实际应用价值。

**关键词：**DDRII SDRAM；FPGA；FIFO；IP核；分时复用技术

**中图分类号：**U285 : TP39 **文献标识码：**A

## Development of high-speed memory interface application based on FPGA

ZHOU Xiaobo, LI Ruijing, ZHAO Qiang

(School of Electronics and Information Engineering, Beijing Jiaotong University, Beijing 100044, China)

**Abstract:** In order to make convenient interface to the complex sequence interface of high-speed and high-capacity storage medium applications, a new design was proposed for the interface device of storage media with FIFO feature based on DDRII SDRAM by this thesis. At first, the principles and implementation of DDRII SDRAM controller were introduced. Then the memory interface module was designed based on the time-sharing technique of DDRII SDRAM. Finally, the principles of the interface controller module was deeply analyzed and implemented by functional simulation through the Quartus II software and FPGA hardware verification. Through stimulation and verification, the high-speed memory interface controller module based on DDRII SDRAM implemented the bi-directional data transfer and interaction between DDRII memory and FPGA, which was with a certain value of practical application.

**Key words:** DDRII SDRAM; FPGA; FIFO; IP core; time-sharing technique

DDRII SDRAM (Double Data Rate II SDRAM)，第2代同步双倍速率动态随机存储器，具有存储容量大、成本低、接口成熟，并行突发访问时，可以达到较高访问速率的优点。为了提高数据传送速率，这类存储介质采用时钟双沿触发的方式，并且接口时序复杂，即使采用厂商提供的IP核，在与FPGA（现场可编程门阵列）内部逻辑接口相连时一般也不能实现直接对接。需要FIFO特性的存储介质接口设计，让接口信号简单化，与FIFO的接口类似，使信息的交流更加便捷。

## 1 DDRII SDRAM控制器

设计中采用的是ALTERA提供的IP核“DD-

收稿日期：2012-09-19

基金资助：中央高校基本科研业务费专项资金资助（2009JBZ003-4）。

作者简介：周晓波，副教授；李瑞菁，在读硕士研究生。

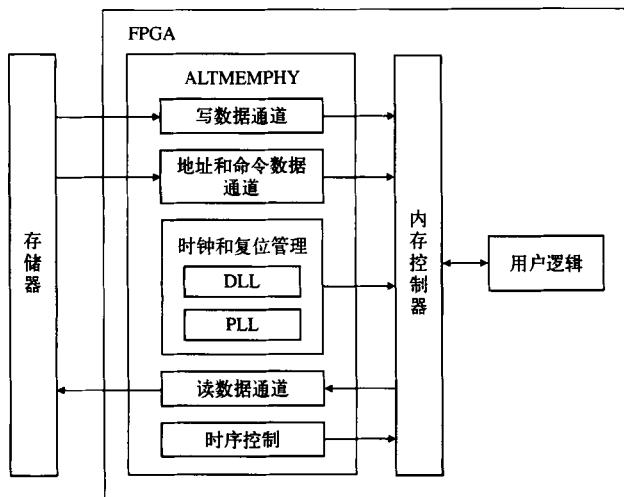

RII SDRAM controller with ALTMEMPHY v10.0”。这个DDRII SDRAM控制器支持多种容量和速度的DDRII SDRAM，并且主要的时间参数均可设置。DDRII SDRAM控制器的原理如图1所示。

DDRII SDRAM控制器IP核用于连接DDRII SDRAM和用户逻辑部分。配合这个DDRII SDRAM控制器，设计了接口控制模块，实现数据在FPGA和DDRII SDRAM之间双向传输与交互的目的。

## 2 设计方案

设计包括：ALTERA DDRII SDRAM控制器IP核，数据产生模块，状态控制模块和数据缓存模块。以下将缓存输入数据和输出数据的FIFO

图1 DDRII SDRAM控制器原理图

简称为WFIFO和RFIFO。

首先，给DDRII SDRAM控制器提供100MHz的锁相环参考时钟，经过这个控制器的锁相环后，生成了150MHz的系统时钟和300MHz的存储器时钟，形成了2个时钟域，达到了高速存储的目的。

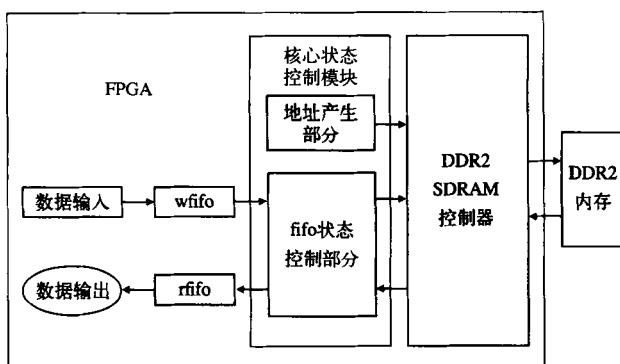

为了测试这个接口模块的正确性，安排了一个输入数据产生模块，将这些数据先缓存在WFIFO中。对DDRII SDRAM的数据总线和地址总线都采用分时复用的方法，经过状态控制模块的控制，在不同时刻将数据从WFIFO写入DDRII SDRAM，以及将数据从DDRII SDRAM读出到RFIFO，再从RFIFO输出。其中，状态控制模块由两部分组成，分别是FIFO状态控制部分和地址产生部分。这个接口模块的原理如图2所示。

图2 接口模块原理图

## 2.1 FIFO状态控制部分

FIFO状态控制部分控制数据在WFIFO、DDRII SDRAM、RFIFO之间的传输过程。在DDRII SDRAM控制器中，有一个重要的信号

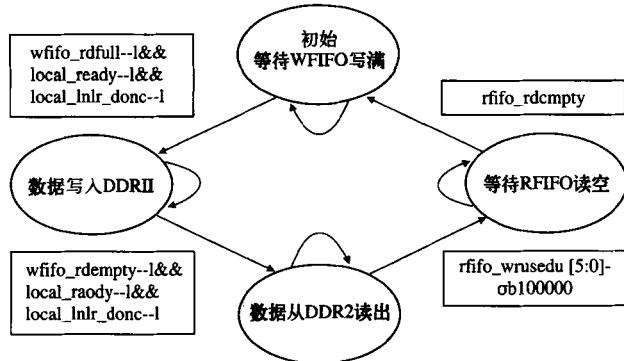

local\_ready，当这个信号有效时，才允许DDRII SDRAM控制器接受读写请求。由于DDRII SDRAM的数据总线只有一组，所以DDRII SDRAM控制器的读写请求信号不能同时有效，需要采用分时复用的技术，根据两个FIFO的空满状态及其内部的数据量来控制数据从WFIFO写入DDRII SDRAM和从DDRII SDRAM读出到RFIFO的传输过程。FIFO状态控制部分的状态转换如图3所示。

图3 FIFO状态控制部分的状态转换图

首先在初始状态，等待WFIFO被写满。当WFIFO被写满，DDRII SDRAM初始化完成并且local\_ready有效时，让WFIFO的读请求和DDRII SDRAM控制器的写请求均有效，控制数据从WFIFO写入DDRII SDRAM。由于WFIFO数据读出的速率比写入快，所以WFIFO中的数据会不断减少。当WFIFO被读空并且local\_ready有效时，让DDRII SDRAM控制器的读请求和RFIFO的写请求均有效，再控制数据从DDRII SDRAM读出到RFIFO。与WFIFO的原理类似，RFIFO数据写入的速率比读出快，所以RFIFO中的数据会不断增加。当RFIFO中的数据量达到一定值时，就不再向RFIFO中写入数据，直到RFIFO被读空时，再转入等待WFIFO写满的状态，进行新一轮的数据传输。

用FIFO的内部数据量状态来控制数据的传输，避免了因为FIFO的溢出而导致数据丢失，保证了数据传输的完整性。

由于DDRII SDRAM数据总线只有一组，写入和读出的数据需要在不同的时间占用这组总线，数据将一组一组输出，每组输出数据中间都有一段时间处于空闲状态，因此加了一个有效数据指示信号，用于屏蔽空闲状态时输出的无效数据。

## 2.2 FIFO数据缓存单元

根据实际运用的需要,本设计在FPGA中采用两个小容量的FIFO,来完成数据输入和输出时的缓存与位宽转换。利用ALTERA的FIFO IP核,实现了数据深度为32 M,数据位宽在128 bit和256 bit之间的转换,并可实时输出FIFO内部的实际数据量。FIFO的接口信号由读写时钟、读写请求、数据总线、空满状态信号4部分组成。当读写请求信号有效时,数据在相应时钟的上升沿,临时通过数据总线写入或者读出FIFO。其空满状态能实时显示当前FIFO内部的数据量,以便控制其读写请求信号,避免因为FIFO溢出而导致的数据丢失。

## 2.3 地址产生部分

DDRII SDRAM的寻址结构是按照Bank、Row、Column 3组地址总线的形式进行线性寻址的。线性寻址是指DDRII SDRAM控制器的地址总线只需要接收按照Bank、Row、Column顺序从高到低排列的地址。设计采用27 bit的地址总线。其中,有3 bit宽的Bank地址,每个Bank下可以进行14 bit宽的Row地址寻址,最底层是10 bit宽的Column地址。这部分主要是用选择器和计数器的嵌套程序,完成Bank、Row、Column地址的递增和进位。让这个27 bit的地址总线从0开始累加到限定的最大值,以此记录DDRII SDRAM的读写地址。

因为DDRII SDRAM的地址总线只有一组,所以在对DDRII SDRAM进行读、写操作时,需要分时复用这组地址总线,分别记录读、写操作的DDRII SDRAM地址。在DDRII SDRAM控制器IP核的写请求和local\_ready均有效时,写地址总线开始按照以上规则递增寻址;在DDRII SDRAM控制器IP核的读请求和local\_ready均有效时,读地址总线开始递增寻址。将这两组条件写成或的关系,读写地址的寻址操作就可以用同一段程序来表示,从而达到DDRII的地址总线分时复用的效果。

为了读出前一状态写入的数据,则要保证读地址和之前的写地址有一样的起始位置,所有设置了地址复位信号。当控制器写请求与控制器读请求均为“0”时,地址复位信号为“0”;当控制器写请求与控制器读请求有一个为“1”时,地址

复位信号为“1”。当全局复位信号和地址复位信号为低时,输出给控制器的Bank、Row、Column地址均置为“0”。当从写入状态转入读出状态时,输出给控制器的Bank、Row、Column地址也均置为“0”。

## 3 软件仿真与硬件验证

### 3.1 软件仿真

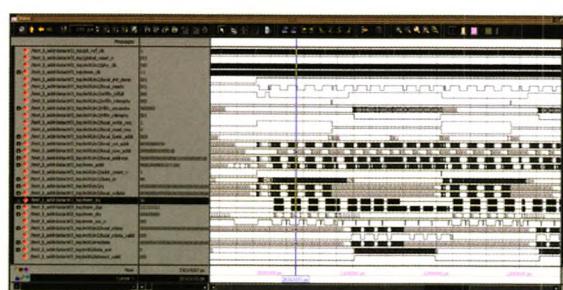

本设计先通过Quartus II软件,结合DDRII SDRAM仿真模型,对接口模块进行功能仿真。

图4 Quartus II软件的接口模块功能仿真(1)

图5 Quartus II软件的接口模块功能仿真(2)

图6 Quartus II软件的接口模块功能仿真(3)

首先,将数据输入到FPGA中。由于mem\_dq是DDRII SDRAM的双向数据传输总线,所以需要采用分时复用的方法在不同时间进行数据的

写入和读出操作。在每一个传输周期，mem\_dq 都有两段相同的数据，第 1 段是写入 DDRII SDRAM 中的数据，第 2 段是从 DDRII SDRAM 读出的数据。图 4 表明数据写入 DDRII SDRAM 时的情况，图 5 表明数据从 DDRII SDRAM 读出时的情况，并且这两幅图在 mem\_dq 上数据相同时有一样的存储器地址 mem\_addr，说明读出了刚才写入时所占用存储单元中的数据，DDRII SDRAM 写入和读出时的寻址操作正确。图 6 表明输入的数据正确地出现在输出数据总线 data\_out 上，实现了 FPGA 和 DDRII SDRAM 之间的双向数据传输与交互。

### 3.2 硬件验证

在 Arria II GX 系列 EP2AGX260FF35C6 型号的 FPGA 开发板上对此设计方案进行硬件验证，并结合 ALTERA FPGA 的在线、片内信号分析工具 SignalTap II 逻辑分析仪进行在线调试。

输入数据的 SignalTap II 波形捕获图如图 7 所示。输入数据是从“1”开始，每逢系统时钟上升沿来临时，输入数据做加 1 操作。图 8 是输出数据的 SignalTap II 波形捕获图。从图中看出，输出数据和输入数据一致，达到了 FPGA 和 DDRII SDRAM 之间数据双向传输与交互的目的。

图7 输入数据的SignalTap II波形捕获图

图8 输出数据的SignalTap II波形捕获图

软件的仿真和硬件的验证都证明此接口模块可行，验证了通过这个接口控制模块，DDRII 内存与 FPGA 之间的双向数据传输与交互的正确性。

### 4 结束语

该设计在 Quartus II 软件的功能仿真和 FPGA 硬件上都得到了验证，这种基于 DDRII SDRAM 的 FIFO 特性存储介质接口装置的开发满足需求的时序功能设计要求，达到了 DDRII 内存与 FPGA 之间的双向数据正确传输与交互的目的，实现了现代电子领域对高速大容量存储介质的需要，使 DDRII 存储介质结合接口控制模块实现了便利的使用。

### 参考文献：

- [1] 李原. DDR/DDR2 接口的 FIFO 设计 [D]. 西安：西安电子科技大学，2009.

- [2] 舒展. DDR2 控制器 IP 的设计与 FPGA 实现 [D]. 安徽：合肥工业大学，2009.

- [3] 针对 Spartan-3 FPGA 的 DDR2 SDRAM 存储器接口 [DB/CD]. Xilinx. 2007.

- [4] DDR2 SDRAM 操作时序规范 [DB/CD]. 三星. 2008.

- [5] External Memory Interface Handbook [DB/CD]. Altera. 2011, 6.

- [6] 徐欣，周舟，李楠，孙兆林. 基于 DDR2 SDRAM 的高速大容量异步 FIFO 的设计与实现 [J]. 中国测试，2009, 35 (6) : 34-37.

- [7] 吴继华，王诚. Altera FPGA/CPLD 设计（高级篇）[M]. 北京：人民邮电出版社，2005.

- [8] 王诚，吴继华. ALTERA FPGA/CPLD 设计（基础篇）[M]. 人民邮电出版社，2005.

- [9] 夏宇闻. Verilog 数字系统设计教程 [M]. 2 版. 北京：北京航空航天大学出版社，2008, 6.

- [10] Quartus II 自带在线逻辑分析仪 SignalTap 的简易使用方法 [DB/CD]. ZTE.

责任编辑 徐侃春