文章编号: 1005-8451 (2009) 01-0042-04

# 铁路无线通信便携式语音记录与中继系统设计

王 麦

(北京交通大学 电子信息工程学院, 北京 100044)

**摘要:** 基于铁路无线列调通信系统, 研究并设计了一款便携式语音记录和中继设备, 从而实现无缝接入铁路无线列调通信系统, 使其网内所有无线组网设备中的模拟语音都转化为数字语音并以语音文件形式存储于SD存储卡上实现记录功能, 还可以通过微机检索方式查询记录下来的语音文件。该设备还能在不影响网内其他设备正常工作的情况下, 对接收到的有效信号进行再生放大, 达到中继的目的, 从而提高系统通信质量, 增加系统通信距离。

**关键词:** 录音; 中继; ARM7; FPGA; SD

**中图分类号:** TP302.1 **文献标识码:** A

## Design of Railway Wireless Communications portable voice recording and Relay System

WANG Qian

(Institute of Electronics and Information Engineering, Beijing Jiaotong University, Beijing 100044, China)

**Abstract:** Based on Train Dispatch Radio Communication, it was researched and designed a portable recording voice and relay equipment, consequently achieve seamlessly accessing to Train Dispatch Radio Communication System—such that all equipments in the Wireless Networking System transferred the analog voice from the digital voice recording passing through by this equipment, and through this device without affecting the other network equipment to work, renewable and zoom in the effective received signal to relay. the purpose of this was enhancing the quality of communications systems, increasing the communications system's distance.

**Key words:** recording; repeater; ARM7; FPGA; SD

在铁路通信这个比较特殊和重要的领域, 对语音工作的发生过程需要有个准确可靠的记录过程。虽然, 目前有些列调设备配备了相应的录音设备, 但是, 其录音的过程完全依赖与无线通信设备, 无法直接无缝的接入无线列调通信系统。无线通信设备体积庞大、造价昂贵、记录方式陈旧, 自动化程度差, 存储量小, 查询不便, 成本高, 效率低, 很难满足用户实际的需求。另外, 系统中其他的组网设备, 如中继器、手持台等, 目前都还没有记录语音的功能。

本文基于铁路无线列调通信系统, 研究并设计一款便携式语音记录和中继设备, 该设备具有较高的移动灵活性, 较强的适应性和通用性, 能够适用于多种环境和场合; 能够无缝接入铁路无线列调通信系统, 不干扰原有系统正常工作和使用, 使其网内所有无线组网设备都可以通过本设备对模拟语音实现数字化记录功能, 即对通话进行

期监控录音并将通话内容转换为数字信息, 以语音文件形式存储于存储介质上。

### 1 系统主要功能

#### 1.1 弱场中继

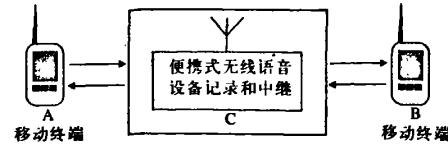

当一个射频单元接收到有效的无线模拟信号后, 控制另外一个射频单元转发该音频信号。实现中继转发模拟无线通话的功能。如图 1。

图 1 中继功能示意图

在既有无线通信系统中, 两移动终端 A、B 间直接加入 C 设备 (便携式无线语音记录和中继设备), 由于系统中增加了 C 设备而使 A、B 间由于长距离或者弯曲隧道的原因而无法进行通话, 通

话质量差的现象都得到解决。

## 1.2 话音记录

对语音信号进行数字化处理，即对通话进行同期监控录音，将通话内容转换为数字信息，以语音文件形式存储于 SD 存储卡上。

### 1.3 实时监听功能

可以通过喇叭对当前通话的通道进行实时监听，监听时不会影响通话，也不会影响录音质量。

### 1.4 自动备份功能

当检测 SD 卡的剩余空间达到设定的范围时，系统便自动删除过期的录音文件，保证一个工作日可能会使用的最大存储空间。

## 2 系统体系结构

### 2.1 系统硬件结构

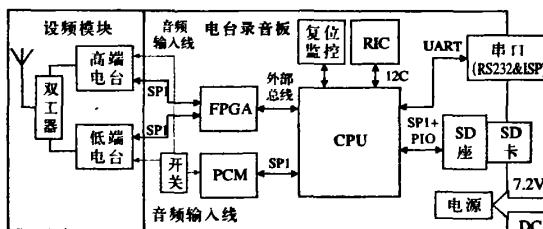

系统的硬件组成结构如图 2。

图 2 系统的硬件组成结构

射频模块部分包括一个双工器，把高端和低端电台信号合路到一个射频天线上。高端和低端电台的音频输入输出线环接起来，高端电台收到的语音通过低端电台发送出去，低端电台收到的语音又通过高端电台发送出去。电台配置、状态信息通过 SPI 接口与 CPU 连接。电台为主 SPI，CPU 为从 SPI。使用一片小型 FPGA 扩展两个 SPI 和发送请求线。CPU 使用 8 位外部总线与 FPGA 通信。电台的音频输出线同时接入 ADPCM 芯片，将语音采样、量化和压缩编码后形成压缩的数字语音，CPU 通过 SPI 口读取 ADPCM 芯片中的语音数据。CPU 对 SD 卡读写操作也采用 SPI 接口。SD 卡中文件的时间由外扩的 RTC 提供。复位电路提供 CPU 和整板的上电复位。串口 UART0 调试时作为调试信号的输出接口，同时也可作为 CPU 程序的烧写接口。

电源 7.2V DC 输入，通过几个 LDO 变换出系统内部芯片所需要的 3.3V、2.5V、1.8V、1.2V。

## 2.2 系统软件结构模式

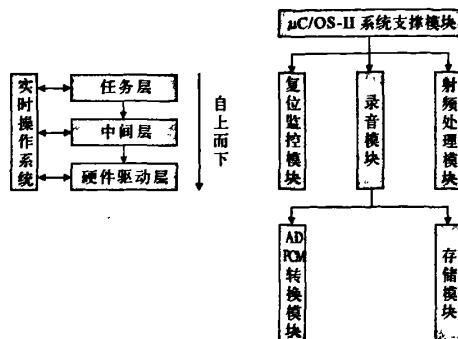

系统软件设计结构如图 3。

图 3 系统软件设计结构图

嵌入式软件设计的原则，从系统的角度分析，整个软件在实时操作系统的支撑下，采用三层结构多任务的方式编写。软件自顶向下的分为任务层、中间层和硬件驱动层。任务层是用户自行定义的业务模块；中间层是连通任务层和硬件驱动层的桥梁，任务层可以不直接调用硬件驱动层，软件编写者完全可以不必了解硬件是如何工作的，仅通过调用中间层就完成业务工作；硬件驱动层提供和硬件相关的条件配置、相关函数、硬件相关协议控制和最终供其它层调用的 API 函数，具体采用那些模块可以根据需要自行调整。

如图 3，本软件主要包括系统支撑模块、复位监控模块、射频处理模块和录音模块。其中，录音模块又包含 4 个子模块，有文件系统模块、ADPCM 转换模块、SD 存储模块和 RTC 模块。

这种软件设计思路，减轻了软件编写的难度，增加了软件的可读性，提高了软件模块的通用性，也降低了查找软件 bug 的工作量。更重要的是，应用这种方法设计的软件不会由于硬件的原因导致系统的功能挂死，另外，本设计中还单独设计了一个复位监控模块，此模块是专门用来防止系统死机状态的。

## 3 关键技术研究

在本系统中由于使用了 SD 卡，ADPCM 采样

编码芯片和射频模块，上述几个模块的对外接口控制均为 SPI 总线接口。众所周知，ARM7 系列目前所生产的微控制器只提供 2 个 SPI 接口，在实际应用中，系统实时性要求较高的情况，2 个电台 SPI 总线接口需要实时和处理器之间进行数据交换通信，而同时 ADPCM 芯片开始录音的时候会和处理器、SD 卡的 SPI 接口间也会实时交互数据，因此该部分不能使用 SPI 接口复用技术。所以，限于本系统 SPI 资源比较紧张，必须增加 SPI 总线，因此，本系统选择采用 FPGA 来实现 SPI 总线接口。

### 3.1 系统描述

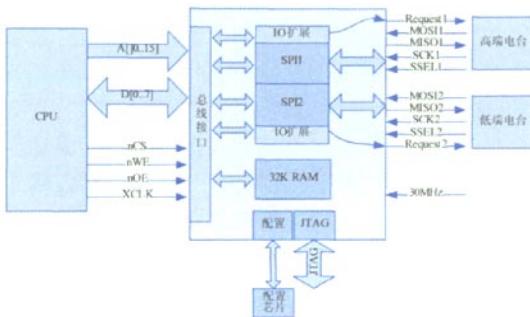

基于本系统功能需求，电台模块工作在 SPI 主机模式，CPU 工作在从机模式，因此，FPGA 设计的 SPI 要工作于从机模式，即在主机 SCK 信号的控制下，按照 SPI 接口规范接收或者发送数据。

FPGA 与 CPU、电台间的连接框图 4。

图 4 FPGA 与电台、CPU 间的接口和 FPGA 内部功能图

CPU 总线接口：实现 CPU 外部总线与内部各个模块接口。

IO 扩展：扩展与电台间发送请求 IO 控制线。

SPI 模块：与电台的 SPI 时序逻辑接口。

### 3.2 电台接口描述

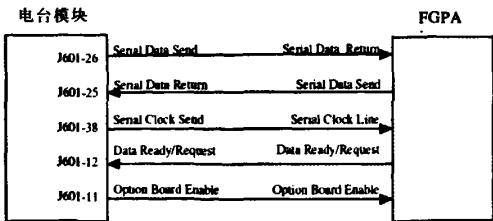

如图 5，电台模块通过 5 线和 FPGA 相连，除 Data Ready/Request 外，其它 4 线为标准 SPI 接口。

图 5 电台与 FPGA 接口

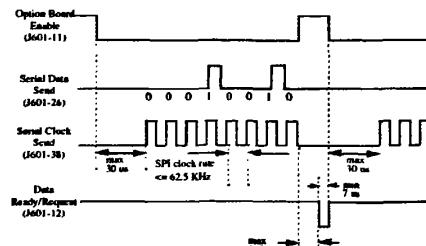

电台主动向 FPGA 发数的通信时序图 6，电台先将 Option Board Enable 置为低电平，30 μs 内在 Serial Clock Send 上发出时钟信号，数据线 Serial Data Send 上开始移出数据。一个字节数据即 8 个 SCK 发送完毕后电台将 Option Board Enable 置高，当 FPGA 检测到 Option Board Enable 被置为高电平后 100 μs 内，相应的将 Data Ready/Request 置为低电平，最少需保持 7 μs 后重新设置为高电平，提示电台模块可以继续发送下一个字节。重复上述操作，直到一条完整的数据指令发送完毕。

图 6 电台向 FPGA 发数时序图

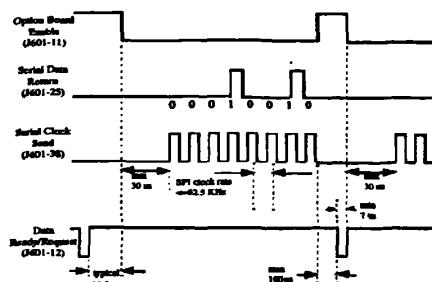

FPGA 主动发起通信时序如图 7，先将 Data Ready/Request 置为低电平，并保持最少 7 μs 间隔后重新置为高电平，然后 16.5 ms 后电台模块将 Option Board Enable 置低，30 μs 内电台在 Serial Clock Send 上发出时钟信号，数据线 Serial Data Return 上开始移出数据。一个字节数据即 8 个 SCK 发送完毕后电台将 Option Board Enable 置高，当 FPGA 检测到 Option Board Enable 被置为高电平后 100 μs，又将 Data Ready/Request 置为低电平，提示电台模块继续接收下一个字节。重复上述操作，直到一条完整的数据指令发送完毕。

图 7 FPGA 向电台发数时序图

### 3.3 仿真

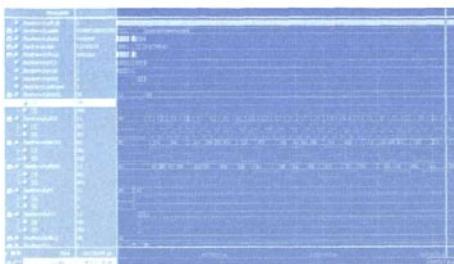

设计使用VerilogHDL语言编写,采用RTL级设计方法,在ModelSim里进行仿真,仿真结果如图8。对SPI0接口仿真,将其设置为从机模式,SSEL平时为高电平、SCK平时为低电平,当SSEL被拉低后,向移位寄存器中写入一个字节0x52,随着SCK上升沿,在MISO线上看到数据0x52(b01010010)一位一位的移出。在MOSI线上,用仿真模拟连续发送数据0x33,根据SPI特性,在使能的情况下MISO线上显示的是MOSI的数据,根据上述仿真证明用FPGA芯片可以实现SPI接口工作,仿真的波形图上可以清楚的看到上述过程。

图8 FPGA功能模块仿真

部分仿真代码如下:

SPI0\_INIT:

```

begin

nCS=0;

nWE=0;

if(i==0)

begin

addr=SPI0_BASEADDR+1;

din=8'hE0; // 11101000, write into

CTL

end

else

begin

addr=SPI0_BASEADDR+0;

din=8'h52; // write into dout

//din=8'h00; // write into dout

end

#0.1

spi_run=3;

state=SPI0_INIT_WAIT;

end

```

## 4 技术指标

在400 MHz~420 MHz, 450 MHz~470 MHz频率范围内, 输入标准调制信号(1kHz@3kHz频偏), 本设备达到技术参数如下表。

表1 技术参数

| 发射部分       |            |

|------------|------------|

| 输出功率       | 4.5 ± 0.5W |

| 剩余调频       | 40/35dB    |

| 音频失真       | ≤ 5%       |

| 接收部分       |            |

| 灵敏度        | 0.3 uV     |

| 信噪比        | 45/40dB    |

| 音频输出功率     | 500mW      |

| 音频失真(额定功率) | ≤ 5%       |

数字语音: IMA ADPCM

数据率: 32.44 Kbps

录音数据格式: IMA ADPCM 32.44 Kbps

## 5 结束语

本设计最突出的特点,不仅将数字化语音技术应用有无线通信系统中,而且,还实现了对无线信号的再生中继。系统中采用了SD存储卡作为存储介质、采用高性能、低功耗元器件等等,从各个方面都体现了便携、通用、人性化的设计思想。

本设计主要针对的是无线通信设备之间记录往来通话,在以后的工作和学习中,能否将本系统和有线调度中心的录音系统相结合,形成一个完整的录音系统,这样,就能够监测整个铁路无线列调通信系统内全部组网设备之间的往来通话,更好的保障铁路通信系统的安全。

### 参考文献:

- [1] 邵贝贝. 嵌入式实时操作系统uC/OS - II[M]. 第2版. 北京: 北京航空航天大学出版社, 2003, 2-30.

- [2] 周立功. ARM嵌入式系统软件开发实例(一)[M]. 北京: 北京航空航天大学出版社, 2004, 1-152.

- [3] 周立功. ARM嵌入式系统软件开发实例(二)[M]. 北京: 北京航空航天大学出版社, 2006, 275-347.

- [4] EDA先锋工作室. 吴继华, 王诚. 设计与验证Verilog HDL [M]. 北京: 人民邮电出版社, 2006, 10-15.

- [5] Jbhasker. 孙海平等译. Verilog HDL综合实用教程[M]. 北京: 清华大学出版社, 2004, 1-10.