文章编号: 1005-8451 (2011) 11-0008-04

## 城轨列车电路仿真平台的研究与开发

洪宇翔, 郎诚廉

(同济大学 电子与信息工程学院, 上海 200331)

**摘要:** 介绍了城轨列车逻辑电路仿真平台的开发流程。通过对列车电路原理的分析, 利用图形技术与面向对象的方法建立电路仿真模型, 并最终建立列车电路图的输入和显示平台。

**关键词:** 城轨电路; 仿真; 模型

**中图分类号:** U266.26 : TP391      **文献标识码:** A

### Study and development on circuit simulation platform for train of urban transit

HONG Yu-xiang, LANG Cheng-lian

(School of Electronics and Information Engineering, Tongji University, Shanghai 200331, China)

**Abstract:** This paper introduced the development process of logic circuit simulation platform for train of urban transit. By analyzing the principle of train circuit and using the graphics technology and object-oriented approach, it was established the circuit simulation model, and set up the input and the display platform for the circuit eventually.

**Key words:** circuit of urban transit; simulation; model

随着城市轨道交通的快速发展, 传统单一的示教板方式已经越来越不适应发展的需要。为了提高相关人员的技能和素质, 需要给不同车型的电路提供一个通用的输入平台和仿真运行直观显示的可视化平台。城市轨道列车电路图形化仿真研究通过C/C++实现将列车内部电路大量继电逻辑图纸输入计算机, 并按一定要求给定部分状态, 用颜色、位置、形状等信息, 动态地显示列车电路中各种器件的得电及失电状态, 使相关专业人员能够直观、灵活地学习掌握列车电路的工作原理, 了解运行中机车内部工作的状态, 并熟练进行故障判断和处理。

### 1 开发平台的构思

采用计算机图形技术, 把城轨列车电路原理图按一定格式输入计算机并显示在大屏幕显示器或投影机上, 再根据逻辑控制关系, 动态地显示电路在正常或故障情况下各器件的动作变化, 使列车内部电路的工作原理形象、直观地表达出来, 用于原理教学和故障训练。可分为以下步骤: (1) 电路图输入; (2) 生成逻辑关系; (3) 设置状态; (4) 动作显示。

收稿日期: 2011-01-21

作者简介: 洪宇翔, 在读硕士研究生; 郎诚廉, 教授。

#### 1.1 电路图输入

在仿真过程中, 要能动态地显示电路在正常或故障情况下各器件的动作情况以及导线的电流流向, 电路图数据中需包括元件类型、元件标识、元件物理状态与逻辑得电状态、元件引脚的连接关系等属性。为此可将列车电路中的电气元器件作为单个图形元素, 根据元器件的图形特征建立可扩展的元件库(适用于多种型号的列车), 利用交互式绘图技术, 通过鼠标的单击、双击、拖动等简单的动作来绘图, 并实现插入、删除、移动、缩放、旋转等编辑功能。采用滚屏技术, 可以在屏幕上绘制较大的电路图。

#### 1.2 生成逻辑关系

引入有向图的方法自动生成列车电路的逻辑控制模型。把原理图转化为对应的有向图, 通过分析图形数据文件中各对象的相互连接关系, 建立电路的逻辑模型, 找出电路的所有节点和支路。再利用深度优先搜索算法及各元件对象的物理状态、故障状态求取通路。

#### 1.3 设置状态及动作显示

根据现实中的工况及故障情况设置元器件的状态, 利用生成的逻辑回路自动处理电路中开关、触点及线圈信息的变化, 并显示相关电路及支路的得、失电状态。由于电路图分成几个相对独立的部分, 因此系统中得、失电状态的改变是由消息驱动

的。当开关、触点动作,接触器线圈得、失电等事件发生时,都要发出相应的消息给有关的电路。

## 2 列车电路仿真设计

将图形技术、面向对象方法引入系统的建模过程,除了用数学方式描述实际系统外,还直接采用电路图表征系统内部特性的变化过程,从而可以从抽象概念和直观感觉两方面去理解和研究机车电气系统各部分的作用和相互关系。

### 2.1 列车电路的原理分析

城轨列车电路各不相同,根据各种电器设备的功能和作用,电压等级可分为电源、辅助电路和控制电路3个基本独立的电路系统。3种电路通过电-磁、电-空、电-机械传动方式相互联系。列车电路的工作通过改变控制电路中的主令电器的位置控制,电路中的所有器件以及连接它们的导线相互之间有着密不可分的联系,其中许多电器本身又可以分成几个部分,如继电器由线圈和常开、常闭触头组成,各部分可出现在电路图中许多不同的地方,存在耦合关系。

分析列车电路原理时,将列车电路中相对独立的部分当作一个元件处理,这个元件可以是电源、开关等完整的器件;是接触器或继电器的线圈、触头等器件的一部分;是由多个器件组成的合成元件。所有元件只有“通”与“不通”或“得电”与“失电”2种状态,所以可以把列车电路当作逻辑电路处理。把元件的状态分为物理状态和逻辑状态2种。

### 2.2 电路图的生成

电路图中元件较多,绘图时若将元件图形作为可直接操作的最小图形元素,直接对元件整体进行编辑要方便很多。这样,需要为所有元件设置图形模型来完成元件的输入。任何元件图形都是由点、直线和弧线组合而成,图形可以根据各自特征由不同数量以及不同相对位置的点、直线和弧线构造而成。元件图形模型应包含元件在所有状态下的物理特征,通过线型的改变实现元件的动作变化,从而反映显示出元件不同的状态。元件库是元件图形模型的集合,它根据各元件图形的构造特征将图形数据存储在文本文档中,供绘图使用。其格式如下:

|                                                                                                                                                                                                                                                                                                 |                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 总元件数(n)                                                                                                                                                                                                                                                                                         | //16 bit整型,共2 Byte       |

| KindID                                                                                                                                                                                                                                                                                          | //16 bit整型数,共2 Byte      |

| 元件名                                                                                                                                                                                                                                                                                             | //共(字符串长度+1) Byte        |

| l tr b                                                                                                                                                                                                                                                                                          | //选中矩形框;共8 Byte          |

| 点个数 n1                                                                                                                                                                                                                                                                                          | //16 bit整型数,共2 Byte      |

| Point <sub>i</sub> .x Point <sub>i</sub> .y                                                                                                                                                                                                                                                     | //共 n1 × 2 × 2 Byte      |

| 线数 n2                                                                                                                                                                                                                                                                                           | // 16 bit整型数,共2 Byte     |

| Line <sub>i</sub> .style Line <sub>i</sub> .x <sub>1</sub> Line <sub>i</sub> .y <sub>1</sub> Line <sub>i</sub> .x <sub>2</sub> Line <sub>i</sub> .y <sub>2</sub>                                                                                                                                | // 共 n2 × (1+4 × 2) Byte |

| 弧数 n3                                                                                                                                                                                                                                                                                           | // 16 bit整型数,共2 Byte     |

| Arc <sub>i</sub> .style Arc <sub>i</sub> .x <sub>1</sub> Arc <sub>i</sub> .y <sub>1</sub> Arc <sub>i</sub> .x <sub>2</sub> Arc <sub>i</sub> .y <sub>2</sub> Arc <sub>i</sub> .x <sub>a</sub> Arc <sub>i</sub> .y <sub>a</sub> Arc <sub>i</sub> .x <sub>b</sub> Arc <sub>i</sub> .y <sub>b</sub> | // 共 n3 × (1+8 × 2) Byte |

| 引脚数 n4                                                                                                                                                                                                                                                                                          | // 16 bit整型数,共2 Byte     |

| Joint <sub>i</sub> .x Joint <sub>i</sub> .y                                                                                                                                                                                                                                                     | // 共 n4 × 2 × 2 Byte     |

列车电路原理图主要由元件、连接线、标识符3种符号组成,根据仿真要求,需要对它们作完整的描述来反映其特性及参数,采用面向对象的技术分别将这3类符号当作实体对象处理。为此按如下方式定义数据结构来描述。

//标注文字的数据结构

```

struct CMark{

CMark *next;

short cbSize;           //结构体长度

CPoint ref;             //标注框坐标

TCHAR content[1];       //标注内容

CMark *ReSize(int n);

};

```

//元件与连接线实体共用的模板

```

struct CUnit{

CUnit *next;

short cbSize;

CPoint ref;             //在画板上位置

DWORD CellID;           //元件ID号

short KindId;            //类型号

CMark* pMark;           //指向标注框

unsigned int PhState:8;   //物理状态

unsigned int LgState:8;   //元件状态

unsigned int :16;         //预留位

unsigned int :32;         //预留位

};

```

//画板上元件的数据结构

```

struct CCell:CUnit{

```

```

float Scale;                                // 放大倍数

float RotateAngle;                         // 旋转角度

short j_num;                                // 连接点数

struct tagJOINT{ // 元件实体中连接点

Clink *pLink;    // 相连接的 Link 实体

CPoint pt;

}Joint[1];           // 不定长数组

short point_num;

tagPOINT PointArray[1]; // 不定长数组

short line_num;

tagLINE LineArray[1]; // 不定长数组

short arc_num;

tagARC ArcArray[1]; // 不定长数组

};

// 画板上连接线的数据结构

struct CLink:CUnit{

short j_num;                                // 连接点数

struct tagLINKJOINT{

CCell *pCell;    // 与之相连元件实体

short j;          // 实体中第 j 个连接点相连

}Joint[1];

short d_num;

CPoint DotArray[1]; // 不定长数组

short polynum;

struct tagPOLYLINEINFO{ // 连接实体中

char style;

CPoint PolyPoint[4];

}PolyArray[1];

};

}

```

绘图时，通过点击相应按钮或图标来选择元件，把它移动到相应位置，并添加与之关联的标注，再通过捕捉选定相应的连接点，按一定算法画出连接线，将相关元件连接起来。生成的电路图用结构体数组将对象的位置、状态、连接关系等记录下来，以数据文件的形式存储。

### 3 仿真应用

通过输入元器件的状态，利用生成的逻辑回路自动处理电路中开关、触点及线圈信息的变化，并刷新电路图，显示相关电路及支路的得、失电状态。

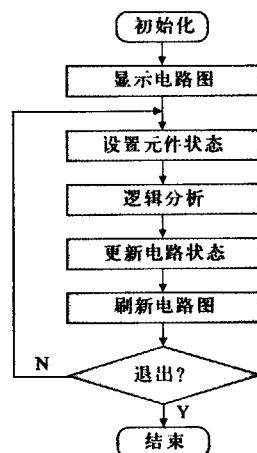

态。其流程如图 1。

图 1 仿真应用流程图

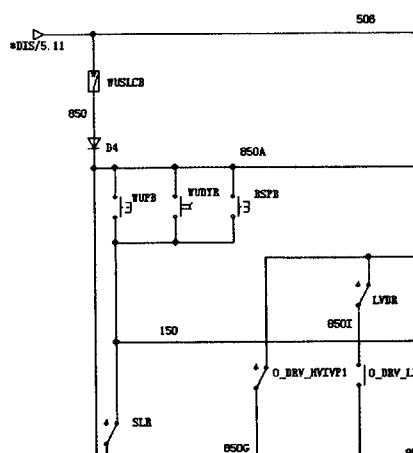

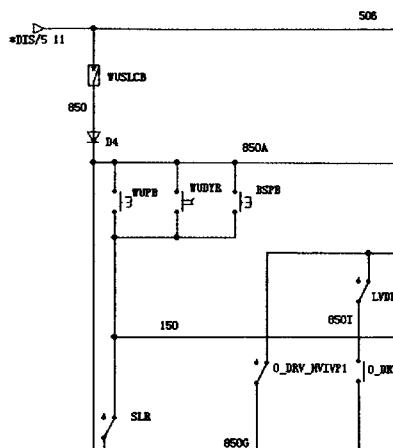

列车电路庞大而复杂，一般将其分成多个模块，便于管理应用。以上海地铁三号线为例，按功能可分为驾驶 (DRV)、紧急制动 (EBR)、照明 (LGT)、受电弓控制(PAN)、气制动(PNE)、列车推进(PRO)、整车管理系统(TIM)、辅助逆变 (AUX)、空调通风(ACV)、通信部分(COM)、电源分配(DIS)、门控制(DOR)等模块，每个模块包含一张或多张电路图，仿真时只针对部分模块显示。上海地铁三号线驾驶 (DRV) 模块唤醒部分电路截图如图 2，初始化断路器 WUSLCB 闭合，按下列车控制按钮 WUPB，经设置传入状态后部分效果如图 3，此时“通”回路所有元件和连接线颜色均显示为红色。

图 2 驾驶模块唤醒部分电路截图

(下转 P13)

定, 即  $n$  固定, 攻击者的能力逐渐增加, 即攻击者控制用于DDoS攻击的僵尸主机数量  $k$  增加, 得到的结果如下。

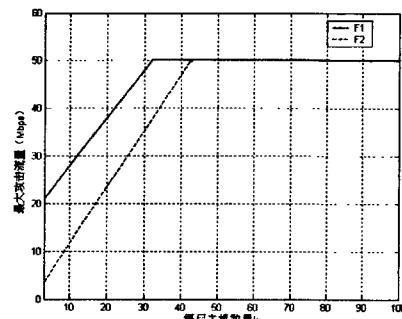

当  $n=100$ , 随着  $k$  的增加,  $F_1$  和  $F_2$  的变化如图3。

图3 攻击流量随僵尸主机数量的变化情况

图3中, 在  $n$  不变的情况下, 随着  $k$  的增加,  $F_1$  和  $F_2$  都不断增加, 但是  $F_2$  始终小于等于  $F_1$ 。  $F_1$  和  $F_2$  的差值逐渐减小, 当攻击者能够制造的攻击流量达到  $T$  时,  $F_1=F_2=T$ , 二者相等。当  $k$  较小时,  $F_1$  与  $F_2$  的差值较大。

这说明在2种网络中, 随着攻击者能够控制的主机数量增加, DDoS攻击对目标主机的攻击流量都会逐渐增大。但是身份与位置分离映射网络中的攻击流量始终不超过传统网络。当攻击者能够控制的主机数量较少时, 身份与位置分离映射网络中的攻击流量与传统网络中的攻击流量相比, 相差较多, 这说明身份与位置分离映射网络对DDoS攻击的缓解作用在攻击者能力不强的情况下

下尤为明显。同时, 在身份与位置分离映射网络中, 要达到与传统网络相同的攻击流量, 攻击者需要控制更多的主机, 才能达到目的。

## 2 结束语

身份与位置分离映射网络能够解决传统互联网存在的诸多问题, 本文分析了它对DDoS攻击的缓解作用。随着对身份与位置分离映射网络研究的不断深入, 其相对于传统互联网的优势将愈发明显, 是未来网络的发展方向, 有着广阔的发展及应用前景。

### 参考文献:

- [1] Jose N. DDoS Attack Evolution [J]. Network Security, 2008 (7): 7-10.

- [2] David C, Robert B, Aaron F, Venkata P. FARA: Reorganizing the Addressing Architecture. Proc. Proceedings of the ACM SIGCOMM workshop on Future Directions in Network Architecture (FDNA)[C]. Karlsruhe, Germany, August 2003, pp. 313-321.

- [3] 张宏科, 苏伟. 新网络体系基础研究——一体化网络与普适服务[J]. 电子学报, 2007, 35 (4): 593-598.

- [4] Wu-chun F, Hurwitz, J, Newman H. Optimizing 10-Gigabit Ethernet for Networks of Workstations, Clusters, and Grids: A Case Study. Proceedings of the 2003 ACM/IEEE conference on Supercomputing[C]. November 2003, pp. 50.

责任编辑 陈蓉

(上接P10)

图3 经设置传入状态部分效果图

## 4 结束语

经测试应用, 该平台能够快速便捷的输入大量城轨列车电路原理图, 可适用于不同型号的列车, 具有较强的可扩展性和可移植性。平台不仅能够用于列车电路原理教学, 还可以用于电路设计和电路逻辑验证等仿真。

### 参考文献:

- [1] 和青芳. 计算机图形学原理及算法教程[M]. 北京: 清华大学出版社, 2005.

责任编辑 陈蓉