文章编号: 1005-8451(2007)12-0042-03

## 列车综合无线通信平台主控单元的设计

李憬然<sup>1</sup>, 唐祯敏<sup>1</sup>, 宋水<sup>2</sup>, 王旸<sup>2</sup>

(1.北京交通大学 电子信息工程学院, 北京 100044; 2.北京首科中系希电信技术有限公司, 北京 100044)

**摘要:** 介绍一种新型的列车无线通信设备的主控单元。系统采用基于INTEL XSCALE架构的PXA270处理器, 对外扩展多个串口, 与通信平台的各个功能模块进行数据交换, 加以控制。详细论述系统软、硬件平台的搭建, 并重点说明对外串口扩展部分。

**关键词:** 主控单元; PXA270; 串口扩展; 软件平台; 硬件平台

中图分类号: TP39 文献标识码: A

### Desing of main control module used in locomotive communication platform

LI Jing-ran<sup>1</sup>, TANG Zhen-min<sup>1</sup>, SONG Shui<sup>2</sup>, WANG Yang<sup>2</sup>

(1. College of Electronics and Information Engineering, Beijing Jiaotong University, Beijing 100044, China;

2. Beijing Xi-Dian Information Technology Co, Ltd, Beijing 100044, China)

**Abstract:** A new controller of wireless communication equipment was introduced. The System was used the PXA270 CPU based on the INTEL XSCALE frame. For communicating with the functional modules, the controller was expanded multi-serials external. The hardware and the software flat were detailedly described, and the section of serials expanding was stressed.

**Key words:** main control module; PXA270; serials expanding; software flat; hardware platform

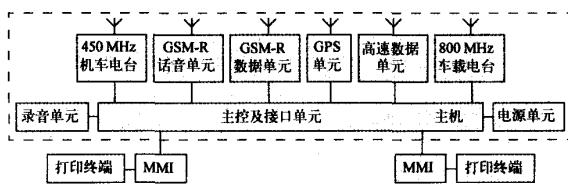

自上世纪 90 年代以来, 我国铁路已经进行了多次大规模的提速。现在一些主干线上列车的最高时速已经达到 200 km/h。以前的 450 M 通信设备已经不能适应高速环境, 为此我们自主研发了一个新型的基于 GSM-R 网络的综合无线通信平台(CIR)。本文详细论述了通信平台的主控单元。通信平台结构示意图如图 1。

图 1 通信平台结构示意图

主控单元采用以 Intel XSCALE 架构的 PXA270 处理器为核心的嵌入式平台, 因为考虑到多串口数据收发的稳定性问题, 我们利用 I<sup>2</sup>C 或者标准串口与一片 LPC2129 (ARM7 芯片) 相连接, 用 LPC2129 并行外扩 8 个全功能标准串口, 很好地解决了高速性和稳定性的矛盾, 现场运行反应良好。

收稿日期: 2007-04-08

作者简介: 李憬然, 在读硕士研究生; 唐祯敏, 教授。

### 1 PXA270 芯片特性介绍

PXA270 是一款 32 bit 处理器芯片, 其工作频率可高达 624 MHz。它采用了 Intel Wireless MMX Technology 技术, 提高了多媒体音频和视频的处理能力。PXA270 处理器大体上遵从 ARM 系列芯片指令集, 但是不包含浮点指令。另外, 加入了 SpeedStep 技术的 PXA270 处理器, 可以轻松地达到每秒运行百万条指令的运算能力。

PXA270 内置 4 片 64 kbit 的片内 SRAM。同时, PXA270 向用户提供了双向数据接口, 支持丰富的外部存储器扩展 (FLASH、SDRAM、SD 卡、CIF 卡等)。该处理器最大的特点就是多媒体功能强大, 不仅对外提供音频模块, 还支持最高分辨率达 800 × 600 的 LCD 显示器控制接口扩展。

PXA270 的其他主要功能模块还有: USB 控制模块、I<sup>2</sup>C 外围通信模块、UART 接口、键盘接口、USIM 模块和 PWM 控制模块等等。

### 2 硬件平台设计

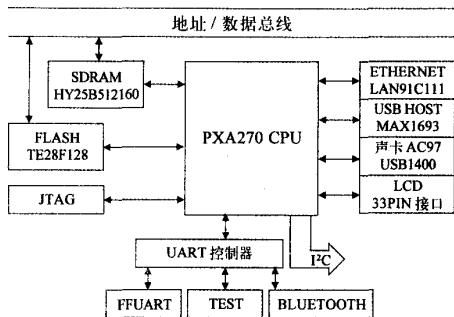

以 PXA270 处理器为核心的硬件平台设计框图

如图 2。

图 2 PXA270 硬件平台设计框图

## 2.1 外部存储器设计

PXA270 为外部静态存储器 (Static Memory) 提供了 6 片选信号接口，最多可接 6 片 FLASH。根据现场需要，主控单元 FLASH 由 2 片 16 bit 的 Intel TE28F128 构成 32 bit 系统，分别由 nCS0 和 nCS1 选中低 16 bit 和高 16 bit，容量达到 32 Mbyte，主要用来存放系统启动加载程序。经测试，完全可以存放如 Win CE、Embedded Linux、QNX、VxWORKS 等主流嵌入式操作系统。该芯片为 NOR 型 FLASH，读写速度分别为 40 M 和 8 M，读写速度较快。

PXA270 处理器的 SDRAM 接口支持 4 个 16 bit 或 32 bit 宽度的分区 (BANK0~BANK3)，每一个分区都被分配了 64 Mbyte 的地址空间。这样，我们最多可以接 4 片 SDRAM。根据实际需求，主空单元的 SDRAM 由 2 片 INFINEON 公司的 HYB512160AC-7.5 构成 32 bit 系统，由片选信号 nSDCS0 和 nSDCS1 分别选择低 16 bit 和高 16 bit，容量为 128 Mbyte，时钟频率为 133 MHz，完全可以满足上述操作系统及上层应用程序的运行。

本系统所有外部存储芯片均直接连接在 CPU 地址/数据总线上，由片选信号时序逻辑加以区分控制。

本系统无外接存储卡的扩展。

## 2.2 通信接口设计

### 2.2.1 UART 接口

系统采用 MAX 系列芯片将 UART 模块转为通用 RS232 串口和 RS422 串口引出，与外围设备通信。

### 2.2.2 USB 接口

PXA270 处理器集成了 USB HOST 和 USB CLIENT。我们选用 MAX 系列芯片，并根据现场实际情况，只对 USB HOST 做了设计，可外接 U 盘 (或 FLASH)，作为与外界数据交换的一种方式。

### 2.2.3 网络接口

本系统采用一片 10 M/100 M 的 LAN91C111NE 网卡芯片，支持 32 bit 系统。数据地址总线直接连接到片上，通过 nCS4 (属于 Static Memory Controller) 片选信号和一些控制信号对网卡的读写进行操作。网口通信是本系统与外界进行数据交换的主要模式之一。因可靠性的要求，还在这一部分添加了一块 EEPROM (1 024 bit) 作为一些数据的缓存。

### 2.2.4 I<sup>2</sup>C 接口

PXA270 处理器内置了 400 Kb/s 的 I<sup>2</sup>C 模块，可以用作系统的扩展。本系统用 I<sup>2</sup>C 与一片 ARM7 相连接进行双向数据通信。(ARM7 在另一块电路板上，相对独立但受 270 控制。下文将详细介绍。)

## 2.3 串口的扩展

根据现场的稳定性需求，采用外扩一片 LPC2129 (ARM7) 芯片进行串口扩展。2129 与主 CPU 通过 I<sup>2</sup>C 或高速串口通信，相对独立但受 PXA270 控制。LPC2129 共 64 个 GPIO 引脚，其中 8 个 IO 作为片选，8 个 IO 作为中断控制信号 (EINT[0~3]，共 8 个独立外部中断)，控制 8 个串口 (TTL 形式)。TTL 串口由并行串口扩展芯片 SC16C554 (1 × 4，共 2 片) 引出，再经由背板插座，转换为标准 422 串口，达到与外围功能模块通信的目的。

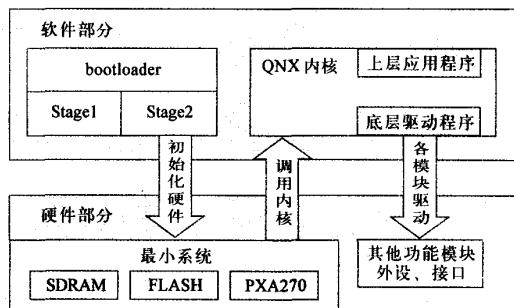

## 3 软件平台设计

软件平台设计框图如图 3。

图 3 软件平台设计框图

### 3.1 系统引导程序 u-boot

Boot loader 的实现依赖于 CPU 体系结构。本系统根据 PXA270 的结构及特性，选用 u-boot 作为系统的引导程序 boot loader。U-boot 是开源且功能强大的 boot loader，支持多种处理器，如 PowerPC、

ARM、MIPS 和 x86 等，在嵌入式系统设计中的应用广泛。

我们将 u-boot 分成两部分来描述：stage1 和 stage2。将硬件初始化代码和一些依赖于硬件的代码放在 stage1 中，用汇编语言来实现，尽量短小精悍；stage2 则由 C 语言来实现，可以完成复杂的功能，并增强了代码的可读性和可移植性。

### 3.1.1 内存地址分配

PXA270 处理器将静态存储器分为 6 个 64 MB 的区域，地址 0x0000\_0000 到 0x1400\_0000。系统启动时先将这些静态存储器（FLASH）中的内容映射到 SDRAM 中，偏移地址由 CPU 进行分配。启动加载程序 Boot loader 一般被存放在静态存储器的开头处，以便 CPU 上电或复位时首先调用执行 boot loader。

同步动态存储器分为 4 个 64 MB 的区域（Partition0~3），从地址 0xA000\_0000 到 0xAC00\_0000。可以单独动作，也可以 2 个 BANK 一组构成 32 bit 系统。其中 BANK0 和 BANK1 为一组，BANK2 和 BANK3 为一组，分别进行操作。可以用 1 片、2 片或 4 片 SDRAM 芯片，当使用 2 片时，只能由 nSDCS0/nSDCS1 或者 nSDCS2/nSDCS3 其中的一组片选信号来选中芯片。

执行完上述步骤，u-boot 便完成了对系统硬件的初始化和操作系统的加载。

### 3.2 嵌入式操作系统 QNX

PXA270 处理器支持大多数主流嵌入式操作系统，根据现场对实时性可靠性的要求，本系统采用了 QNX 操作系统。QNX 是一个实时、微核、基于优先级、消息传递、抢占式多任务、多用户和具有容错能力的分布式网络操作系统。

QNX 实时操作系统一个开放的系统，其应用程序接口完全符合 POSIX 标准。这样，其他诸如 Linux 等操作系统的程序代码就可以很容易地移植到 QNX 上来，极大地扩展了 QNX 操作系统的可用资源。

我们通过编写板级支持代码 BSP，对 QNX6.2.1 的源代码进行移植和剪裁，实现了一个小型化功能强的内核程序，充分发挥了各硬件功能。（最后烧入 Flash 的 QNX 操作系统只有约 2 M）。

### 3.3 各功能模块的驱动程序及上层应用程序

我们对 QNX6.2.1 内核添加了 USB、LCD、声卡和网卡等功能模块的驱动代码。这些代码有些是从互联网上找到的（开源），有些是根据经验编写的。经测试，各模块正常运行，可以达到现场要求。

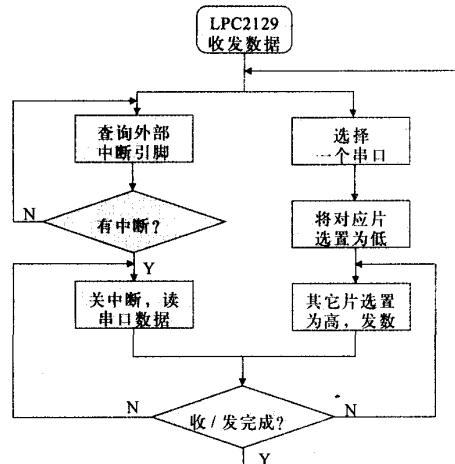

### 3.4 串口扩展部分程序设计

串口扩展是本系统的一大特点，也是系统的关键部分。我们主要通过 LPC2129 芯片来控制 2 片并行串口扩展芯片 SC16C554，进而达到控制 8 个串口的目的。这部分软件流程图如图 4。

图 4 串口扩展软件设计流程

## 4 系统性能分析

本系统构建了一个以 PXA270 处理器为核心的嵌入式平台，对外提供了一些通信接口，如串口、USB、网口和 I<sup>2</sup>C 等，并结合现场需求对串口进行了扩展。经测试这些接口运行正常，8 个 9 600 bps 的全功能串口均未出现数据丢失、延误现象。在主频高（520 MHz），在功能强的前提下，整板功耗在 2 W~3 W，可以说很好地满足了现场的实际需要。

## 5 结束语

本文介绍一种基于 GSM-R 网络的新型铁路通信设备的主控单元。是一个以 PXA270 处理器为核心的嵌入式系统的设计与实现，对 PXA270 处理器的功能应用比较全面，软、硬件设计都是非常经典的。对此系统功能与功耗进行了测试，基本符合设计要求。本文对于 PXA270 处理器的设计开发具有借鉴意义。目前，PXA270 已经在工业控制、多媒体控制、军事工业和航空航天等领域有了广泛的应用。

### 参考文献：

- [1] 傅 峰. Windows CE 嵌入式开发入门—基于 Xscale 架构[M]. 北京：人民邮电出版社，2006.